Ian Main

Ian is a Distinguished Technologist at HP Teradici. Ian has over 15 years of experience at HP Teradici, involved in protocol performance, architectural and security aspects of PCoIP design, and customer requirements analysis, with particular focus on remote graphics intensive workflows. Follow Ian on Twitter! https://twitter.com/PCoIP_Ian

This is the fourth post in a technical blog series by Ian Main, Teradici's Technical Marketing Principal. In the series, he'll go through the PCoIP Ultra protocol enhancements from a technical perspective, and answer common questions that have come up since the release of the enhancements.

And now without further delay, over to Ian!

PCoIP UltraTM Technical Series Part 4: PCoIP Ultra Efficient CPU Scaling

The previous post introduced the tremendous throughput gains using NVIDIA NVENC GPU offload or taking advantage of AVX2 optimizations. Today, we’ll explain why the AVX2 processor should be thought of as a scalable acceleration unit and how the benefit scales with additional core count.

As a quick side, AVX2 processor extensions are available in most modern servers and workstations – these special registers and instructions enabled some Teradici boffins to pack and process sets of 16 pixels concurrently, on each available core! Previously such gains would have required dedicated silicon co-processors, akin to our original TERA processors. Of course, hand coding the critical areas of the encoder was a significant project, but well worth the effort.

Take a look at the sketch below – even a sluggish ~2 GHz processor with 16 cores is capable of 16 cores x 16 pixels per operation x ~2 operations per cycle x 2 GHz which approaches 1 tera-operations-per-second. Remarkable!

This brings us to another marketing slide from our PCoIP Ultra launch campaign which, at least conceptually, shows the relationship between encoder design and throughput:

Left: We show our original SSE2 encoder which is available in VMware Horizon. This single-threaded implementation is well suited to VDI workloads which demands high image quality but not generally high pixel throughput.

Center: Teradici Cloud Access Software improved on the throughput with the SSE4.2 implementation, which includes multi-threading support up to approximately 8 threads, beyond which efficiency is diminished.

Right: The PCoIP Ultra AVX2 enhancements are shown. Assuming 16 processor cores shown, the encoder leverages all available AVX2 engines which provides dual benefits of distributing the encoding workload and maximizing the CPU availability to application software. In other words, the PCoIP-AVX2 encoder operates as a thin layer between operating system and application. The more cores available, the lower the impact on your application.

At the processing detail level, we divide each image frame into multiple small tiles of pixels which allows us to use all the AVX2 engines of a multi-core CPU in a concurrent fashion. Each free AVX2 engine is assigned a tile, processes it quickly and immediately assigns another tile which accelerates overall throughput. We add some processing wizardry to prevent image discontinuities known as blocking artifacts along tile boundaries – a common problem with tile-based image processors.

To illustrate AVX2 CPU scaling…

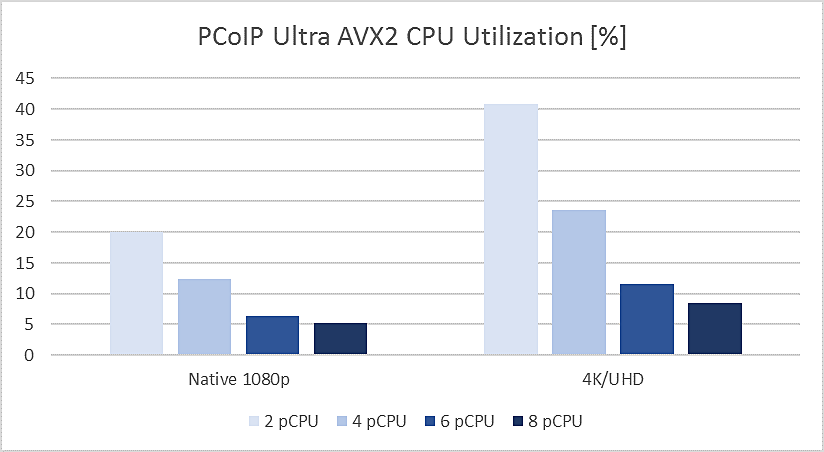

I ran a handful of PCoIP Ultra benchmarks on a dual processor 3.5 GHz Xeon server (8 physical cores) at different core counts (pCPU) – comparing looped playback of the opening scene of Big Buck Bunny (24 fps version) at native 1080p to playback at full-screen 4K/UHD:

For the 4K/UHD workload on the right, a dual core workstation comfortably handles 30 fps video playback but consumes 40% of the CPU, including both VLC Player and PCoIP Agent processes. CPU drops nicely as cores are added to less than 10% when 8 cores are deployed.

For the 1080p workload on the left, a tidy 5% of CPU resources are required using 8 cores. Bearing in mind that these tests were conducted on a mid-life 8 core machine and that Xeon processors about to surpass 50 cores, I see a very low impact encoding future ahead!

Next post:

Stay tuned for a CPU and bandwidth comparison between PCoIP Ultra and the SSE4.2 implementation.

In case you missed it:

Part 1: Top-Level Architecture

Part 2: PCoIP Ultra Client Capability

Part 3: Four Times the Pixel Rate

Ian Main

Ian is a Distinguished Technologist at HP Teradici. Ian has over 15 years of experience at HP Teradici, involved in protocol performance, architectural and security aspects of PCoIP design, and customer requirements analysis, with particular focus on remote graphics intensive workflows. Follow Ian on Twitter! https://twitter.com/PCoIP_Ian

Posts by Tag

- Cloud Access Software (74)

- PCoIP (69)

- Cloud Computing (43)

- Media & Entertainment (40)

- Cloud Access (38)

- HP Anyware (38)

- PCoIP Technology (35)

- Zero Client (30)

- Teradici CAS (29)

- hybrid work (29)

- AWS (27)

- VDI (23)

- PCoIP Zero Clients (22)

- Amazon Workspaces (21)

- NVIDIA (21)

- CAS (20)

- Microsoft (20)

- PCoIP Ultra (20)

- Azure (19)

- Cloud Access Plus (19)

- Microsoft Azure (19)

- Google Cloud (18)

- GPU (17)

- VMware (17)

- Virtualization (15)

- Cloud Desktops (14)

- Remote Workstation (14)

- VFX (14)

- remote work (14)

- Amazon Web Services (13)

- VMware Horizon (13)

- cloud graphics (13)

- digital workspaces (13)

- Data Security (12)

- Google (12)

- Cloud Workflows (11)

- Amazon (10)

- Cloud Migration (10)

- End-point Security (10)

- GPUs in the Cloud (10)

- Remote Working (10)

- Virtual Desktops (10)

- DaaS (9)

- protocol (9)

- Autodesk (8)

- Cloud (8)

- Dell (8)

- Ian Main (8)

- Pervasive Computing Platform (8)

- SIGGRAPH (8)

- Security (8)

- virtual workstations (8)

- Cloud Workspaces (7)

- Game Development (7)

- Gaming (7)

- Hybrid Cloud (7)

- Interview (7)

- PCoIP Workstation Access Software (7)

- Remote Display Protocols (7)

- Video Editing (7)

- architecture (7)

- macos (7)

- multicloud (7)

- remote visualization (7)

- 3D graphics (6)

- Architecture Engineering Construction (6)

- Blast Extreme (6)

- Blast Extreme Vs PCoIP (6)

- CAD (6)

- COVID-19 (6)

- Cloud Access Platform (6)

- Collaboration (6)

- Desktop Access (6)

- Events (6)

- H.264 (6)

- HP (6)

- Hardware Accelerator (6)

- Horizon Protocols (6)

- NVIDIA Grid (6)

- Wacom (6)

- remote workforce (6)

- AMD (5)

- AWS re:Invent (5)

- Adobe (5)

- All Access (5)

- CAM (5)

- Cloud Security (5)

- Getting to know... (5)

- IGEL (5)

- Inside Teradici (5)

- NABShow (5)

- PCoIP Management Console (5)

- Q & A (5)

- Remote worksation (5)

- Thin Clients (5)

- Webinar (5)

- coronavirus (5)

- quarantine (5)

- remote graphics (5)

- Cloud Endpoints (4)

- Cybersecurity (4)

- GPU-Accelerated Cloud (4)

- Google Cloud Platform (4)

- HPE (4)

- Linux (4)

- Microsoft Ignite (4)

- N-Series GPU (4)

- NVIDIA GPU (4)

- Randy Groves (4)

- Remote Workspace (4)

- User Experience (4)

- auto offload (4)

- lossless (4)

- mac (4)

- AWS Marketplace (3)

- Amazon Workspace Graphics Bundle (3)

- Anyware Manager (3)

- Architecture, Engineering, and Construction (3)

- AutoCAD (3)

- Avid (3)

- CAD in the Cloud (3)

- Codecs (3)

- Dan Cordingley (3)

- Disaster Recovery (3)

- GCP (3)

- GTC (3)

- Google Cloud Next (3)

- Google Next (3)

- IBC (3)

- Jellyfish Pictures (3)

- LG (3)

- LucasFilm (3)

- Management Console (3)

- Maya (3)

- Microsoft Azure Marketplace (3)

- NAB (3)

- NVIDIA NVENC (3)

- Qumulo (3)

- Remote Desktop (3)

- Sohonet (3)

- Video (3)

- Virtual Machines (3)

- Workstations in the Cloud (3)

- Zero Client Deployment (3)

- broadcasting (3)

- business continuity (3)

- cas manager (3)

- linux desktops (3)

- movie production (3)

- pcoip encoding (3)

- remote workstation card (3)

- vmworld (3)

- zero trust architecture (3)

- 3D Workflow (2)

- AWS Graphics Bundles (2)

- AWS re:Invent 2018 (2)

- Adobe Premiere (2)

- Alex Herrera (2)

- Alta PCoIP Zero Clients (2)

- Amulet Hotkey (2)

- Apple (2)

- Arjen van der Meulen (2)

- Cloud Access Manager (2)

- Customer Story (2)

- DNEG (2)

- David Smith (2)

- EC2 Elastic GPU (2)

- FIPS (2)

- Federal Government (2)

- HP ZCentral Remote Boost (2)

- HTML5 (2)

- Healthcare (2)

- IBC 2018 (2)

- IBC 2019 (2)

- IBM (2)

- ILM (2)

- Industrial Light & Magic (2)

- Microsoft Build (2)

- Moore's Law (2)

- NVIDIA M60 (2)

- NVIDIA RTX6000 GPU (2)

- Oil & Gas (2)

- Scanline (2)

- Trusted Zero Client (2)

- VMworld 2016 (2)

- Workstation (2)

- Workstation Access (2)

- Z by HP (2)

- aws re:Invent 2019 (2)

- cloud solutions (2)

- data scientists (2)

- emmy (2)

- finance (2)

- hammerspace (2)

- lenovo (2)

- macstadium (2)

- omniverse (2)

- partner solutions (2)

- private cloud (2)

- server offload (2)

- tehama (2)

- virtual studio (2)

- wacom tablet (2)

- 10ZiG (1)

- 4K (1)

- 4K UHD Display (1)

- AEC (1)

- AI (1)

- AWS Endpoints (1)

- AWS Outposts (1)

- Adobe After Effects (1)

- Adobe Creative Suite (1)

- Adrian Graham (1)

- Android (1)

- Animation World (1)

- AnythingIT (1)

- Anyware Connector (1)

- Appsbroker (1)

- ArcGIS Pro (1)

- Atomic Cartoons (1)

- Autodesk 3DS Max (1)

- BCCDC (1)

- BVE (1)

- Bandwidth (1)

- Battery Life (1)

- BeBop Technology (1)

- Beaufort Memorial Hospital (1)

- Big Data (1)

- Brown Bag Films (1)

- CEEF16 (1)

- CP Technologies (1)

- CPU Load (1)

- CRN (1)

- Cadalyst (1)

- Careers (1)

- Celebrating 3 Million PCoIP Zero Clients (1)

- Certificate Management (1)

- Chris Feeney (1)

- Christus Health (1)

- Chrome (1)

- Chromebook (1)

- Cisco (1)

- Clearcube (1)

- Cloud Expo Europe (1)

- Cloud Expo Europe 2016 (1)

- Cloud Foundry Foundation (1)

- Compute (1)

- Connection Health Monitor (1)

- Crafty Apes (1)

- D-Wave (1)

- DISRUPT (1)

- DISRUPT EUC (1)

- DISRUPT Unite (1)

- DISRUPT2019 (1)

- DSB Consulting (1)

- Data Center 100 (1)

- Dell EMC (1)

- Disaster Recovery Plan (1)

- Disney (1)

- Don Listwin (1)

- EUC (1)

- Education (1)

- Elastic GPU (1)

- Emanuel Pirker (1)

- End User Computing (1)

- Esri (1)

- Event (1)

- Facebook (1)

- Fairfield Energy (1)

- Forbes (1)

- Forrest Smith (1)

- G3 Instances (1)

- GIS (1)

- General Availability (1)

- Google Cloud Marketplace (1)

- Google Marketplace (1)

- Government (1)

- Guest Post (1)

- HP RGS (1)

- HP t310 Quad-Display Zero Client (1)

- HP t310 Zero Client (1)

- HPA (1)

- HPE LoadRunner (1)

- HPE ProLiant (1)

- Hewlett Packard Enterprise (1)

- Higher Education (1)

- Hollywood Professional Association (1)

- Hyperclouds (1)

- IT Business Edge (1)

- Imprivata (1)

- Imprivata OneSign (1)

- Intel (1)

- Intel oneAPI Rendering Toolkit (1)

- Jeff Groudan (1)

- Jensen Huang (1)

- Jeremy Smith (1)

- Jon Peddie Research (1)

- Karan Batta (1)

- LDAP (1)

- MESA (1)

- Martin Traute (1)

- Mason City Clinics (1)

- Meltdown (1)

- Metro Health (1)

- Microsoft AVD Deployment (1)

- Mirela Cunjalo (1)

- NAB2017 (1)

- NAB2018 (1)

- NAB2019 (1)

- Neverware (1)

- Nexenta Systems (1)

- Nuke (1)

- OEM (1)

- OpenSDS (1)

- PCoIP Client (1)

- Quad Display (1)

- Quantum Computing (1)

- Rachel Berry (1)

- Rajen Sheth (1)

- Recycle (1)

- Release (1)

- Remote Display Protocol (1)

- SSO (1)

- Sagar Rawal (1)

- Sam Ramji (1)

- Schlumberger (1)

- Single Sign-On (1)

- Softlayer (1)

- Sony Pictures (1)

- Spectre (1)

- Star Wars (1)

- Steve Mueller (1)

- Stratodesk (1)

- Tablet (1)

- Tarkan Maner (1)

- Tech Talk Thursdays (1)

- TechTalk Thursdays (1)

- Tera2 (1)

- Terraform (1)

- The Angry Birds Movie (1)

- The Channel Co. (1)

- The Register (1)

- Thick Clients (1)

- Unigine Heaven (1)

- University of Waterloo (1)

- VDI Server Benchmarks (1)

- VDI Servers (1)

- VMBlog (1)

- VMware Horizon Clients (1)

- Virtual Reality (1)

- Virtualization 50 (1)

- Visualization (1)

- Webinar Series (1)

- Whitepaper (1)

- Work-from-Home Rapid Response Guide (1)

- Wyse (1)

- YOUNGTECH (1)

- Ziad Lamman (1)

- avid media composer (1)

- blade workstation (1)

- brianmadden.com (1)

- cleverDome (1)

- cloud deployments (1)

- community (1)

- connection broker (1)

- covid19 (1)

- dashboard (1)

- fabulatech (1)

- gpu acceleration (1)

- graphics acceleration (1)

- hypervisor (1)

- latency (1)

- leostream (1)

- local termination (1)

- nutanix (1)

- presentation (1)

- project workflows (1)

- promotion (1)

- protocol comparison (1)

- reference architecture (1)

- schools (1)

- studio Q (1)

- survey (1)

- technology partner program (1)

- test & monitoring tool (1)

- training (1)

- usb peripheral support (1)

- validation video (1)

- virtual display devices (1)

- virtual machine (1)

- vmware solution exchange (1)

- vsphere (1)

- webcam support (1)

- windows (1)

- windows virtual desktop (1)

- work from home (1)

- wvd (1)

- zero trust (1)